เมื่อเดือนกรกฎาคมปีที่แล้ว SpacemiT ได้เปิดตัวชิป SoC รุ่น SpacemiT K3 หลังจากนั้น เราได้เห็นข้อมูลระบบและผลการทดสอบ Benchmarks เบื้องต้นเผยออกมาประมาณเดือนมกราคมของปีนี้ ล่าสุดบริษัทได้เปิดตัวบอร์ด K3 Pico-ITX SBC อย่างเป็นทางการ ซึ่งขณะนี้มีวางจำหน่ายผ่านตัวแทนจำหน่ายหลายแห่งแล้ว นอกจากนี้ Firefly ยังได้เปิดตัวฮาร์ดแวร์ที่ใช้ชิป K3 ในชื่อ AIBOX-K3 ซึ่งเป็นกล่องคอมพิวเตอร์ Edge Computing ระดับอุตสาหกรรมแบบครบชุดที่ใช้สถาปัตยกรรม RISC-V มินิพีซี Edge AI รุ่น AIBOX-K3 ใช้โปรเซสเซอร์ SpacemIT Key Stone K3 แบบ 8 คอร์ และมาพร้อม AI Engine ในตัวที่ให้พลังประมวลผลสูงสุดถึง 60 TOPS ทำให้เหมาะสำหรับงานประมวลผล Local LLM Inference และแอปพลิเคชัน Edge AI ต่าง ๆ สเปคของ Firefly AIBOX-K3 : SoC – SpacemiT K3 CPU 8x 64-bit R […]

SpacemiT K3 Pico-ITX SBC และโมดูล SoM ใช้ชิป RISC-V Octa-core รองรับมาตรฐาน RVA23 พร้อม RAM สูงสุด 32GB และ UFS สูงสุด 256GB

SpacemiT เปิดตัวบอร์ด SBC ขนาด Pico-ITX รุ่น K3 และโมดูล K3-CoM260 อย่างเป็นทางการ โดยใช้ซีพียู SpacemiT K3 X100 แบบ Octa-core ที่รองรับมาตรฐาน RVA23 พร้อมประสิทธิภาพ AI สูงสุด 60 TOPS รองรับหน่วยความจำ LPDDR5 สูงสุด 32GB, สตอเรจ UFS สูงสุด 256GB และรองรับ NVMe SSD ผ่าน PCIe Gen3 x4 ตัวบอร์ดยังมาพร้อมคอนเนกเตอร์ eDP, ช่อง 10GbE SFP+, พอร์ต Gigabit Ethernet RJ45, การเชื่อมต่อไร้สาย WiFi 6 และ Bluetooth 5.2 ในตัว, พอร์ต USB Type-C จำนวน 2 พอร์ต, พอร์ต USB 2.0 จำนวน 4 พอร์ต รวมถึงสล็อต M.2 Key-B ที่ทำงานร่วมกับช่อง NanoSIM สำหรับรองรับการเชื่อมต่อเครือข่าย 4G LTE หรือ 5G และฟีเจอร์อื่น ๆ อีกมากมาย สเปกบอร์ด K3 Pico-ITX SBC: System-on-Module – K3-CoM260 (หรือ Jupiter 2 NX) SoC – SpacemiT K3 CPU 8x 64-bit RISC-V X10 […]

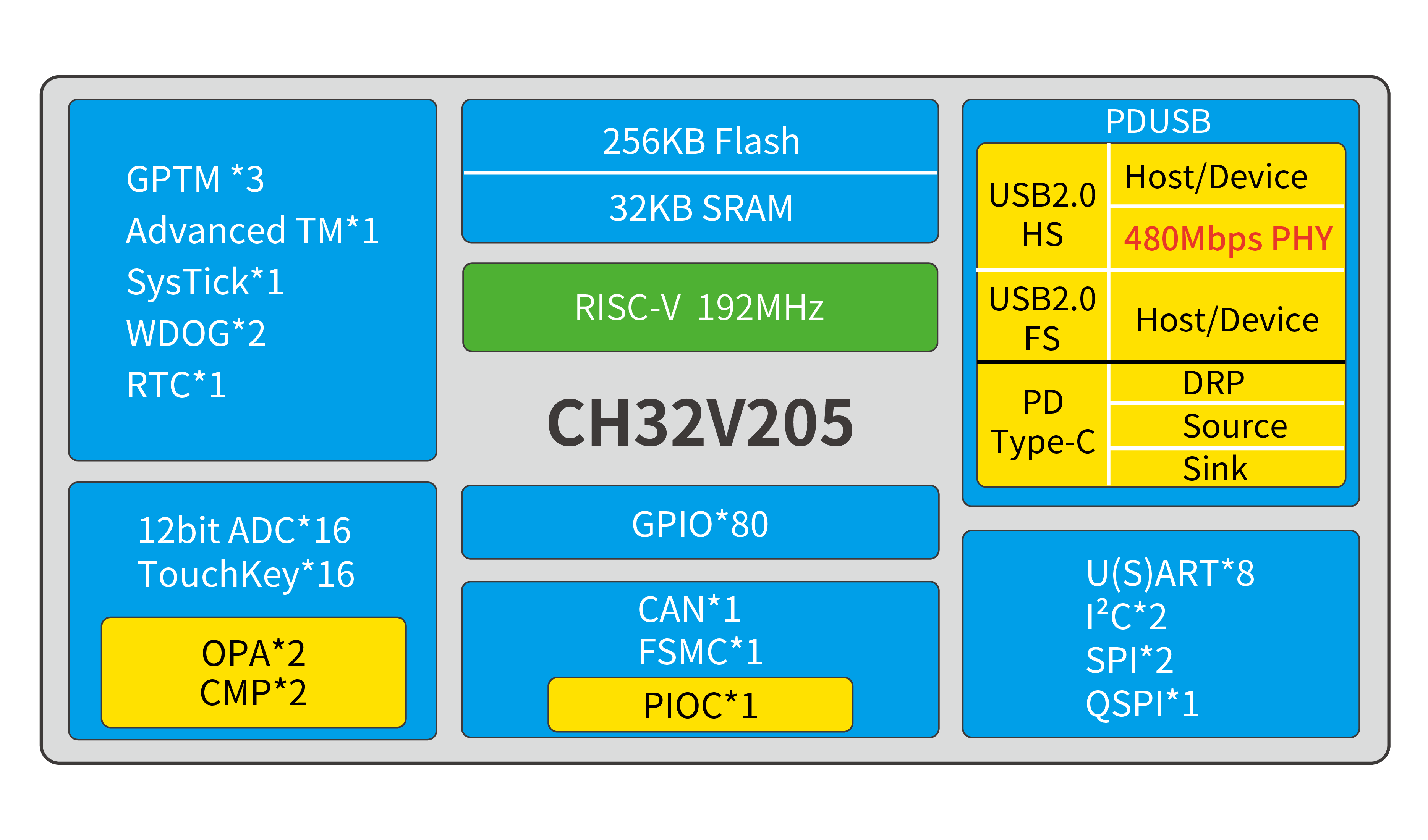

WCH CH32V205 : ไมโครคอนโทรลเลอร์ RISC-V 192 MHz พร้อม USB 2.0 High-Speed 480 Mbps

WCH CH32V205 เป็นชิปไมโครคอนโทรลเลอร์แบบ 32 บิต สถาปัตยกรรม RISC-V ที่ทำงานด้วยความถี่สูงสุด 192 MHz มาพร้อมหน่วยความจำ SRAM ขนาด 32KB และ flash 256KB รวมถึงอินเทอร์เฟซ USB 2.0 แบบความเร็วสูง (High-Speed) ที่รองรับโหมด Host/Device พร้อม PHY ในตัว ที่ความเร็ว 480 Mbps ไมโครคอนโทรลเลอร์รุ่นใหม่นี้ยังมีอินเทอร์เฟซ USB 2.0 แบบ Full-Speed (12 Mbps) อีกหนึ่งชุด ที่รองรับทั้งโหมด Host และ Device รวมถึงพอร์ต USB PD, ขา GPIO จำนวน 80 ขา, ADC ความละเอียด 12 บิต จำนวน 16 ช่องสัญญาณ, อินเทอร์เฟซ TouchKey จำนวน 16 ช่อง และยังรองรับอินเทอร์เฟซอื่น ๆ เช่น CAN Bus, USART, I2C, SPI และ QSPI สเปคของ WCH CH32V205 : MCU core – โปรเซสเซอร์ QingKe แบบ 32 บิต สถาปัตยกรรม RISC-V3B ความเร็วสูงสุด 192 MHz หน่วยความจำและสตอเรจ SRAM ขนาด […]

Linux 7.0 เปิดตัวแล้ว พร้อมการเปลี่ยนแปลงที่น่าสนใจ

Linus Torvalds ได้ประกาศเปิดตัว Linux 7.0 อย่างเป็นทางการผ่าน Linux Kernel Mailing List (LKML), ก่อนหน้านี้ประมาณสองเดือน ได้มีการเปิดตัว Linux 6.19 ซึ่งมีการเปลี่ยนแปลงสำคัญหลายประการ เช่น การเข้ารหัสลิงก์ PCIe และการยืนยันตัวตนอุปกรณ์แบบปลอดภัย, การปรับปรุงระบบไฟล์ BTRFS และ EXT4 รวมถึง API สำหรับ color pipeline ที่รองรับ HDR ตลอดจนการเปลี่ยนแปลงอื่น ๆ อีกมากมาย สำหรับ Linux 7.0 นั้น ไม่มีฟีเจอร์เฉพาะที่โดดเด่นเป็นพิเศษ และไม่ได้ถือว่าเป็นการออกรุ่นใหญ่ (major release) แต่อย่างใด เพียงแต่โดยปกติแล้ว Linus จะทำการอัปเดตหมายเลขเวอร์ชันหลักเมื่อถึงเลข 19 ดังนั้นจึงกลายเป็น Linux 7.0 แทนที่จะเป็น Linux 6.20 การเปลี่ยนแปลงที่น่าสนใจใน Linux 7.0 การเปลี่ยนแปลงที่น่าสนใจบางส่วน ได้แก่: เอกสารเกี่ยวกับ AI Coding Assi […]

บอร์ด WeAct CH32V006F8U6 Mini Core ราคาประมาณ 65 บาทที่ใช้ MCU RISC-V และรองรับ I/O 3.3V/5V

บอร์ด WeAct CH32V006F8U6 Mini Core เป็นบอร์ดพัฒนาขนาดจิ๋ว ราคาประหยัด ที่ใช้ไมโครคอนโทรลเลอร์ CH32V006 RISC-V ความถี่ 48 MHz โดยมาพร้อมพอร์ต USB-C ปุ่มรีเซ็ต และขา I/O แบบ headers 2 แถว (แถวละ 12 พิน) ซึ่งรองรับแรงดันไฟได้ทั้ง 3.3V และ 5V บริษัท WCH ได้เปิดตัว CH32V006 ในปี 2024 เพื่อเป็นรุ่นอัปเกรดจาก CH32V003 ที่ได้รับความนิยม โดยเพิ่มหน่วยความจำมากขึ้น (SRAM จาก 2KB เป็น 8KB) และหน่วยเก็บข้อมูล (Flash จาก 8KB เป็น 62KB ) รวมถึงมี GPIO มากขึ้น รองรับช่วงแรงดันไฟที่กว้างขึ้น และใช้แกนประมวลผล 32-bit RISC-V2C ที่ได้รับการปรับปรุง ก่อนหน้านี้ยังไม่ค่อยพบบอร์ด CH32V006 จากผู้ผลิตรายอื่น แต่บอร์ดจาก WeAct Studio นี้ได้เข้ามาเติมเต็มช่องว่างดังกล่าว สเปคของบอร์ด WeAct CH32V006F8U6 Mini Core : SoC – WCH CH32V006F8U6 […]

Telink TL3228 : MCU ไร้สาย แบบ dual-core RISC-V ประหยัดพลังงาน รองรับ Bluetooth 6.0 และ 802.15.4

Telink เปิดตัวตระกูลไมโครคอนโทรลเลอร์ไร้สาย TL322x โดยเริ่มจากรุ่น TL3228 ซึ่งมาพร้อม MCU แบบ dual-core RISC-V , ความถี่ 192 MHz รองรับการสื่อสารหลากหลาย ได้แก่ Bluetooth 6.0, Matter, Thread, Zigbee, RF4CE และโปรโตคอล 2.4GHz แบบ proprietary เหมาะสำหรับงาน Smart Home, การติดตามทรัพย์สิน (asset tracking), อุปกรณ์เกมมิ่งระดับ “8K” และอื่น ๆ ชิปรุ่นนี้ยังรองรับฟีเจอร์ใหม่ของ Bluetooth เช่น Channel Sounding, AoA/AoD และ LE Audio รวมถึงเทคโนโลยี HDT ของบริษัทที่ให้ความเร็วรับส่งข้อมูลสูงสุด 6 Mbps และมีค่าหน่วงต่ำมาก (ultra-low latency) สเปคของ Telink TL3228 : ซีพียูแบบ Dual-core คอร์ 32-bit Andes D25F RISC-V พร้อม FPU ความถี่สูงสุด 192 MHz คอร์ 32-bit Andes N22 RISC-V หน่วยความจำ – SRAM ขนาด 384 KB สตอเรจ – NVM ขนา […]

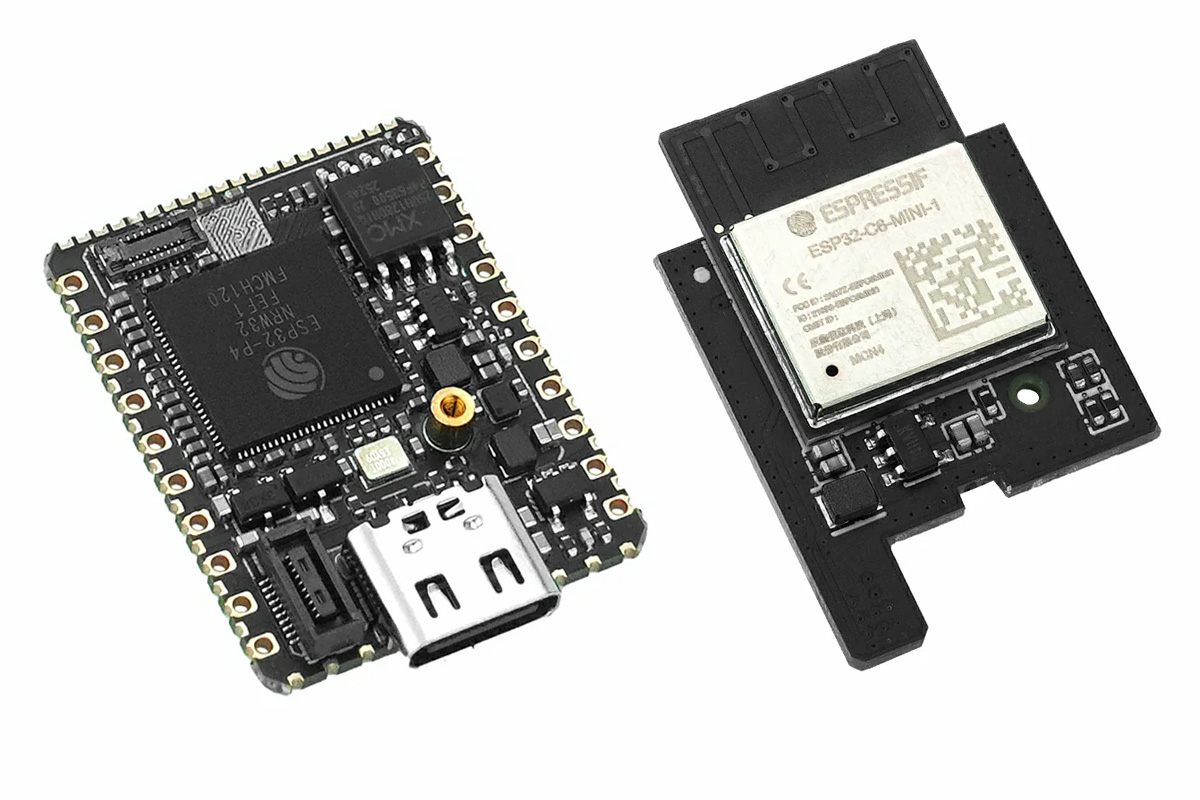

M5Stack Stamp-P4 : บอร์ด USB-C ขนาดจิ่วที่ใช้ ESP32-P4 พร้อมรองรับ Wi-Fi 6 และ Bluetooth 5.4 ผ่านโมดูลเสริม

M5Stack เปิดตัว Stamp-P4 เป็นบอร์ดพัฒนาแบบ USB-C ขนาดจิ๋ว ที่ใช้ชิป ESP32-P4 ซึ่งเป็นไมโครคอนโทรลเลอร์สถาปัตยกรรม RISC-V ประสิทธิภาพสูง โดยมาพร้อมหน่วยความจำ Flash ขนาด 16MB และ PSRAM ขนาด 32MB และยังสามารถรองรับ Wi-Fi 6 และ Bluetooth 5.4 ได้ (ออปชันเสริม) ผ่านโมดูล Stamp-AddOn C6 ที่ใช้ ESP32-C6-MINI-1 แม้จะมีขนาดเล็กเพียง 29.8 x 22.0 x 4.3 มม. แต่ Stamp-P4 ก็รองรับอินเทอร์เฟซที่หลากหลาย ได้แก่ พอร์ตกล้องแบบ MIPI-CSI, อินเทอร์เฟซจอแสดงผล MIPI DSI, Ethernet แบบ RMII, USB 2.0 High-Speed และ GPIO สูงสุดถึง 44 ขา ผ่านขาเชื่อมต่อแบบ castellated holes ระยะพิทช์ 1.27 มม. / 2.00 มม. รวมถึงรู through-hole บางส่วน สเปคของ M5Stack Stamp-P4 : SoC – Espressif Systems ESP32-P4NRW32 CPU Dual-core RISC-V microcontroller @ 360 […]

Alibaba XuanTie C950 : คอร์ RISC-V แบบ 64 บิตประสิทธิภาพสูง รองรับมาตรฐาน RVA23 สำหรับงาน Edge AI

Alibaba ได้เปิดตัว XuanTie C950 ซึ่งเป็น CPU IP แบบมัลติคอร์ 64 บิตประสิทธิภาพสูง มาพร้อมสถาปัตยกรรมไมโครแบบ out-of-order superscalar รองรับมาตรฐานโปรไฟล์ RVA23 และสนับสนุน “ส่วนขยายเสริมทั้งหมด” เช่น Vector Crypto, Zacas และ Zama16 บริษัทยังระบุว่า XuanTie C950 รองรับชุดคำสั่งเฉพาะของตนเองคือ XuanTie AME (Attached Matrix Extension) ISA และสามารถทำงานร่วมกับ IP สำหรับเร่งการประมวลผล AI อย่าง XuanTie TPE (Tensor Processing Engine) ได้, คอร์ RISC-V แบบ 64 บิตรุ่นใหม่นี้จะถูกนำไปใช้ใน SoC ที่มีได้สูงสุด 8 คอร์ต่อหนึ่งคลัสเตอร์ โดยมุ่งเป้าไปที่งานประสิทธิภาพสูง เช่น Cloud Computing, Edge Computing และ AI Computing สเปคของ XuanTie C950 : สถาปัตยกรรม – โปรไฟล์ RVA23 คอร์ประมวลผล – สูงสุด 8 คอร์ ความเร็ว 3.2 GHz; ประส […]