เมื่อเดือนที่แล้ว ฉันได้รับบอร์ดพัฒนา Microchip PolarFire SoC FPGA Icicle development kit ที่มี PolarFire SoC FPGA พร้อมด้วย ระบบย่อย RISC-V CPU แบบ Penta–core 64 บิต และ FPGA ที่มี 254K LE และบูตไปยังระบบปฏิบัติการ Linux ที่ติดตั้งไว้ล่วงหน้าบน OpenEmbedded

วันนี้ ฉันจะสาธิตวิธีเริ่มต้นใช้งาน Yocto BSP และใช้เกณฑ์มาตรฐาน EEMBC CoreMark และฉันจะตรวจสอบ FPGA ด้วย Libero SoC Design Suite ในบทความต่อไป

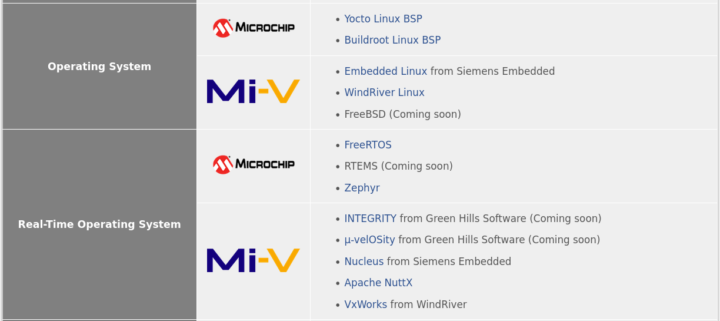

ระบบปฏิบัติการที่รองรับโดย PolarFire SoC FPGA

ความคิดเริ่มต้นของฉันคือจะทำการทดสอบบน RISC-V คอร์โดยใช้ Linux ตรวจสอบข้อมูลระบบบางอย่าง, เรียกใช้การทดสอบเกณฑ์มาตรฐาน (เช่น SBC-Bench) รวบรวมเคอร์เนล Linux และติดตั้งบริการต่างๆ เช่น LEMP stack (Linux, Nginx (ออกเสียงว่า Engine-X), MySQL, PHP) ซึ่งสามารถใช้กับโฮสติ้ง WordPress ได้ แต่แล้วฉันก็ตรวจสอบระบบปฏิบัติการที่รองรับ Microchip PolarFire SoC FPGA

Microchip รองรับ Yocto Linux BSP และ Buildroot Linux BSP , และ การกระจาย Linux แบบฝังตัว ของบริษัทอื่น เช่น Siemens Embedded และ WindRiver มีรายงานว่า FreeBSD กำลังเปิดตัวเร็วๆ นี้ และอาจมีระบบปฏิบัติการแบบเรียลไทม์หลายระบบสำหรับเคอร์เนล RISC-V 64 บิตขนาดเล็กของ SoC

ซึ่งหมายความว่าไม่มีตัวจัดการแพ็คเกจและไม่มีระบบไฟล์รูทที่ใช้ Debian ยกเว้นเครื่องมือบางอย่างที่ฉันวางแผนจะใช้ ในทางทฤษฎีแล้ว ยังคงสามารถบรรลุสิ่งที่ตั้งใจจะทำได้ ฉันไม่ต้องใช้เวลามากถึง 100 ชั่วโมงในการบรรลุเป้าหมายนั้น… ดังนั้นฉันจึงลดความทะเยอทะยานลง และรายงานประสบการณ์ของฉันในการสร้างภาพ Yocto Image คอมไพล์ข้าม Hello world และคอมไพล์และรันการทดสอบเกณฑ์มาตรฐาน EEMBC นี่ไม่ใช่ครั้งแรกที่ฉันเล่นกับ Yocto Project แต่ฉันยังคงได้เรียนรู้บางสิ่งและหวังว่าคุณจะทำได้เช่นกัน

การสาธิตเว็บเซิร์ฟเวอร์และการวิเคราะห์แรงดัน/กระแส

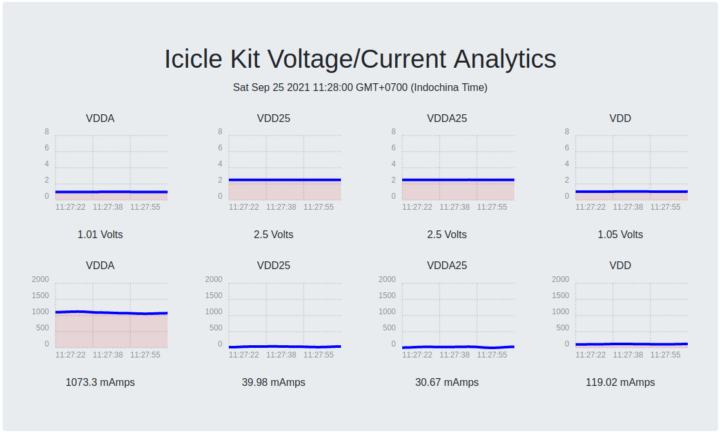

ก่อนทำงานกับ Yocto BSP ฉันได้เชื่อมต่อบอร์ดพัฒนากับอีเทอร์เน็ตเพื่อกรอกคู่มือเริ่มต้นใช้งานของ Microchip ให้สมบูรณ์ และเรียกใช้เว็บเซิร์ฟเวอร์

|

1 2 |

$ cd /opt/microchip/iiohttpserver $ ./run |

เราสามารถเข้าถึงหน้าเว็บที่จะแสดงแรงดันและกระแสไฟของ VDDA (XCVR Tx/Rx Lanes Supply), VDD25 (PLL และ PNVM Supply), VDDA25 (XCVR PLL Supply) และ VDD (Core Supply) โดยไปที่ http:/ /<board_ip_address>

เมื่อเราเรียกใช้เกณฑ์มาตรฐาน EEMBC CoreMark แล้ว การเข้าถึงหน้าเว็บนี้ใหม่จะเป็นเรื่องที่น่าสนใจ

Yocto Linux BSP

มาสร้าง Linux โดยใช้ Yocto BSP ตามที่อธิบายใน Github สำหรับการอ้างอิง ฉันใช้โน๊ตบุ๊คที่ใช้ Ubuntu 20.04 และฉันต้องเปลี่ยนคำสั่งบางคำสั่ง

ขั้นแรก ให้ติดตั้งยูทิลิตี้ repo:

|

1 2 3 4 |

export REPO=$(mktemp /tmp/repo.XXXXXXXXX) curl -o ${REPO} https://storage.googleapis.com/git-repo-downloads/repo gpg --keyserver hkps://keyserver.ubuntu.com --recv-key 8BB9AD793E8E6153AF0F9A4416530D5E920F5C65 curl -s https://storage.googleapis.com/git-repo-downloads/repo.asc | gpg --verify - ${REPO} && install -m 755 ${REPO} ~/bin/repo |

จากนั้นมีการพึ่งพาบางอย่าง:

|

1 |

sudo apt install python3-distutils libyaml-dev libelf-dev chrpath diffstat |

เวลาในการเริ่มต้น repo:

|

1 |

~/bin/repo init -u https://github.com/polarfire-soc/meta-polarfire-soc-yocto-bsp.git -b master -m tools/manifests/riscv-yocto.xml |

ตอนนี้เราสามารถกำหนดค่า build ได้:

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 |

. ./meta-polarfire-soc-yocto-bsp/polarfire-soc_yocto_setup.sh /home/jaufranc/edev/Microchip/yocto-dev expect is already installed at the requested version (5.45.4-2build1) expect is already installed at the requested version (5.45.4-2build1) No packages will be installed, upgraded, or removed. 0 packages upgraded, 0 newly installed, 0 to remove and 9 not upgraded. Need to get 0 B of archives. After unpacking 0 B will be used. spawn sudo dpkg-reconfigure -freadline dash sudo] password for jaufranc: Configuring dash ---------------- The system shell is the default command interpreter for shell scripts. Using dash as the system shell will improve the system's overall performance. It does not alter the shell presented to interactive users. Use dash as the default system shell (/bin/sh)? [yes/no] yes Init OE ### Shell environment set up for builds. ### You can now run 'bitbake <target>' Common targets are: core-image-minimal core-image-full-cmdline core-image-sato core-image-weston meta-toolchain meta-ide-support You can also run generated qemu images with a command like 'runqemu qemux86'. Other commonly useful commands are: - 'devtool' and 'recipetool' handle common recipe tasks - 'bitbake-layers' handles common layer tasks - 'oe-pkgdata-util' handles common target package tasks Adding layers NOTE: Starting bitbake server... NOTE: Starting bitbake server... NOTE: Starting bitbake server... NOTE: Starting bitbake server... NOTE: Starting bitbake server... NOTE: Starting bitbake server... Creating auto.conf To build an image run --------------------------------------------------- MACHINE=icicle-kit-es bitbake mpfs-dev-cli --------------------------------------------------- Buildable machine info --------------------------------------------------- Default MACHINE=icicle-kit-es * icicle-kit-es: Microchip Polarfire SoC Icicle Kit Engineering Sample, emmc/sd boot. * qemuriscv64: The 64-bit RISC-V machine --------------------------------------------------- Bitbake Image --------------------------------------------------- * mpfs-dev-cli: MPFS Linux console-only image with development packages. * core-image-minimal-dev: OE console-only image, with some additional development packages. * core-image-minimal: OE console-only image * core-image-full-cmdline: OE console-only image with more full-featured Linux system functionality installed. * qemuriscv64: The 64-bit RISC-V machine --------------------------------------------------- |

ในการเริ่ม build ให้รันคำสั่งต่อไปนี้:

|

1 |

MACHINE=icicle-kit-es bitbake mpfs-dev-cli |

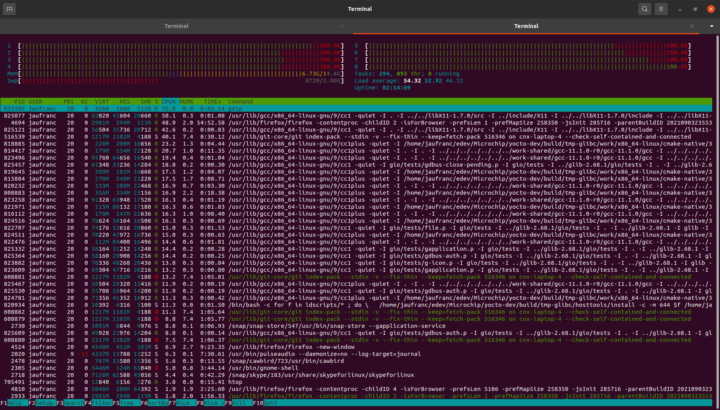

ฉันจำได้ว่าประมาณ 10 ปีที่แล้ว ระบบ Yocto build อาจต้องใช้เวลามากในการสร้างภาพบนแล็ปท็อประดับล่างกว่า 24 ชั่วโมง และด้วยการตั้งค่าเริ่มต้น โน๊ตบุ๊คของฉันซึ่งใช้โปรเซสเซอร์ AMD Ryzen 7 2700U แบบ 8 คอร์ และติดตั้ง RAM ขนาด 16 GB ซึ่งทำให้ช้าลงอย่างรวดเร็วและเกือบใช้งานไม่ได้กับโหลด CPU 50+:

ฉันปล่อยให้งาน build เริ่มต้น หลังจากที่ฉันเข้านอน แต่ฉันไม่ได้ตรวจสอบข้อกำหนดในการจัดเก็บข้อมูล และงาน build จะหยุดหลังจากนั้นประมาณสองชั่วโมง เนื่องจากฮาร์ดไดรฟ์ของฉันหมด ตามที่เราจะเห็นเมื่อการสร้างเสร็จสิ้น จำเป็นต้องมีพื้นที่เก็บข้อมูลฟรีประมาณ 100 GB

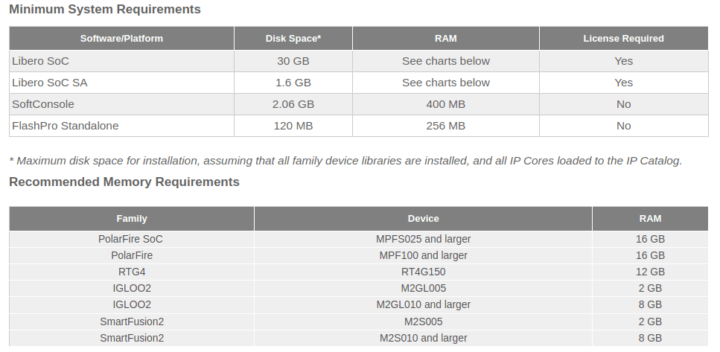

ในขณะที่เราอยู่ในหัวข้อความต้องการของระบบ ชุดออกแบบ Libero SoC จะต้องการพื้นที่เพิ่มเติมประมาณ 35 GB และสำหรับการพัฒนา PolarFire SoC ต้องมี RAM อย่างน้อย 16 GB ดังนั้น คุณจึงต้องการมีเวิร์กสเตชันอันทรงพลังเพื่อพัฒนาแอปพลิเคชันบนชุดพัฒนา PolarFire SoC FPGA Icicle ที่มี RAM มากมายและที่เก็บข้อมูลเพียงพอ

กลับไปที่การ Yocto build ของเรา อุดมคติคือการมีเซิร์ฟเวอร์ build โดยเฉพาะ แต่ถ้าคุณตั้งใจที่จะใช้คอมพิวเตอร์ของคุณพร้อมกับการ bulid คุณอาจต้องการแก้ไข [your_yocto_build_dir]/conf/local.conf

|

1 2 |

BB_NUMBER_THREADS = "4" PARALLEL_MAKE = "-j 4" |

|

1 |

source setup-environment ./your_build_folder |

ก่อนเริ่ม build…

อีกทางเลือกหนึ่งคือการหยุด ด build ชั่วคราวด้วย Ctrl-Z ซึ่งทำงานในลักษณะเดียวกันกับ Ctrl-C แต่ใช้ SIGTSTP แทน SIGINT เพื่อหยุดกระบวนการชั่วคราว และไม่ยุติกระบวนการ

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 |

time MACHINE=icicle-kit-es bitbake mpfs-dev-cli Loading cache: 100% | | ETA: --:--:-- Loaded 0 entries from dependency cache. Parsing recipes: 100% |##########################################| Time: 0:01:43 Parsing of 2381 .bb files complete (0 cached, 2381 parsed). 3667 targets, 166 skipped, 0 masked, 0 errors. NOTE: Resolving any missing task queue dependencies Build Configuration: BB_VERSION = "1.51.0" BUILD_SYS = "x86_64-linux" NATIVELSBSTRING = "ubuntu-20.04" TARGET_SYS = "riscv64-oe-linux" MACHINE = "icicle-kit-es" DISTRO = "nodistro" DISTRO_VERSION = "nodistro.0" TUNE_FEATURES = "riscv64" meta = "HEAD:14795ee305f3c11fcc31cc7ca815b8ff1020e29a" meta-oe meta-python meta-multimedia meta-networking = "HEAD:dcb9ecc1e5720c9614b1cd27575e1e4886dff5c1" meta-riscv = "HEAD:35d1d5849294ff9f2fb98b90657bbf7a1e532d0d" meta-polarfire-soc-yocto-bsp = "HEAD:3c53ffcae8ac86686a53cd15b4541fc7eca1e36f" NOTE: Fetching uninative binary shim http://downloads.yoctoproject.org/releases/uninative/3.1/x86_64-nativesdk-libc.tar.xz;sha256sum=5d0611df544edff6428cef7d871257a91aa6ba1bd92f5365a2df8deb54b6b31e (will check PREMIRRORS first) Initialising tasks: 100% |#######################################| Time: 0:00:11 Sstate summary: Wanted 2529 Local 0 Network 0 Missed 2529 Current 0 (0% match, 0% complete) NOTE: Executing Tasks WARNING: expat-native-2.3.0-r0 do_fetch: Failed to fetch URL https://downloads.sourceforge.net/expat/expat-2.3.0.tar.bz2, attempting MIRRORS if available WARNING: libtalloc-2.3.2-r0 do_fetch: Failed to fetch URL https://www.samba.org/ftp/talloc/talloc-2.3.2.tar.gz, attempting MIRRORS if available WARNING: boost-1.76.0-r0 do_fetch: Failed to fetch URL https://dl.bintray.com/boostorg/release/1.76.0/source/boost_1_76_0.tar.bz2, attempting MIRRORS if available WARNING: htop-3.0.5-r0 do_fetch: Failed to fetch URL git://github.com/htop-dev/htop.git, attempting MIRRORS if available Currently 8 running tasks (5382 of 7084) 75% |####################### | Currently 6 running tasks (6040 of 7084) 85% |########################## | 0: cmake-3.20.1-r0 do_compile (pid 3565535) 72% |#################### | 1: boost-1.76.0-r0 do_compile - 24m44s (pid 3578779) 2: kernel-devsrc-1.0-r0 do_install - 15m17s (pid 3619862) 3: gcc-11.1.0-r0 do_package_write_ipk - 1m23s (pid 3665048) 4: libcheck-0.15.2-r0 do_package_write_ipk - 32s (pid 3669480) 5: libsamplerate0-0.1.9-r1 do_package_write_ipk - 24s (pid 3669801) [1]+ Stopped MACHINE=icicle-kit-es bitbake mpfs-dev-cli real 328m42.945s user 0m0.000s sys 0m0.004s jaufranc@cnx-laptop-4:~/edev/Microchip/yocto-dev/build$ |

เนื่องจาก bitbake ทำให้เกิดกระบวนการอื่นๆ มากมาย เราจึงต้องรอให้กระบวนการเหล่านั้นเสร็จสิ้น และใช้เวลาประมาณ 10 นาทีในการกลับไปใช้คอมพิวเตอร์ตามปกติ

ฉันหยุดไปประมาณ 3 ชั่วโมง แล้วกลับมาทำงานต่อได้ด้วยคำสั่ง “ fg “ มันเหมือนกับโหมดไฮเบอร์เนต สำหรับโปรแกรมเทอร์มินัลและมันก็มีอยู่ตลอดไป แต่ฉันอาจลืมไปหรือไม่เคยใช้เลย การสร้างที่สมบูรณ์ใช้เวลาประมาณ 7 ถึง 8 ชั่วโมงในเครื่องของฉัน

นั่นคือพื้นที่ที่ Yocto BSP ใช้:

|

1 2 3 4 5 6 7 8 |

~/edev/Microchip/yocto-dev$ du --max-depth=1 -h 313M ./.repo 36M ./meta-openembedded 376K ./meta-polarfire-soc-yocto-bsp 6.3M ./meta-riscv 94G ./build 45M ./openembedded-core 94G . |

เราสามารถค้นหารูปภาพใน tmp-glibc/deploy/images/icicle-kit-es/folder:

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 |

ls -lh tmp-glibc/deploy/images/icicle-kit-es/ total 9.8G -rwxr-xr-x 1 jaufranc jaufranc 1.3K Sep 26 18:06 boot.scr.uimg lrwxrwxrwx 2 jaufranc jaufranc 68 Sep 26 18:07 fitImage -> fitImage--5.12.1+git0+ce6fc289da-r0-icicle-kit-es-20210926061423.bin -rw-r--r-- 2 jaufranc jaufranc 4.6M Sep 26 18:07 fitImage--5.12.1+git0+ce6fc289da-r0-icicle-kit-es-20210926061423.bin lrwxrwxrwx 2 jaufranc jaufranc 68 Sep 26 18:07 fitImage-icicle-kit-es.bin -> fitImage--5.12.1+git0+ce6fc289da-r0-icicle-kit-es-20210926061423.bin -rw-r--r-- 2 jaufranc jaufranc 1.7K Sep 26 18:08 fitImage-its--5.12.1+git0+ce6fc289da-r0-icicle-kit-es-20210926061423.its lrwxrwxrwx 2 jaufranc jaufranc 72 Sep 26 18:08 fitImage-its-icicle-kit-es -> fitImage-its--5.12.1+git0+ce6fc289da-r0-icicle-kit-es-20210926061423.its -rw-r--r-- 2 jaufranc jaufranc 4.6M Sep 26 18:08 fitImage-linux.bin--5.12.1+git0+ce6fc289da-r0-icicle-kit-es-20210926061423.bin lrwxrwxrwx 2 jaufranc jaufranc 78 Sep 26 18:08 fitImage-linux.bin-icicle-kit-es -> fitImage-linux.bin--5.12.1+git0+ce6fc289da-r0-icicle-kit-es-20210926061423.bin -rw-r--r-- 2 jaufranc jaufranc 11K Sep 26 18:08 microchip-mpfs-icicle-kit--5.12.1+git0+ce6fc289da-r0-icicle-kit-es-20210926061423.dtb lrwxrwxrwx 2 jaufranc jaufranc 85 Sep 26 18:08 microchip-mpfs-icicle-kit.dtb -> microchip-mpfs-icicle-kit--5.12.1+git0+ce6fc289da-r0-icicle-kit-es-20210926061423.dtb lrwxrwxrwx 2 jaufranc jaufranc 85 Sep 26 18:08 microchip-mpfs-icicle-kit-icicle-kit-es.dtb -> microchip-mpfs-icicle-kit--5.12.1+git0+ce6fc289da-r0-icicle-kit-es-20210926061423.dtb lrwxrwxrwx 2 jaufranc jaufranc 38 Sep 26 18:06 mmc-tftp-icicle-kit-es.txt -> mmc-tftp-icicle-kit-es-v2021.04-r0.txt -rw-r--r-- 2 jaufranc jaufranc 1.2K Sep 26 18:06 mmc-tftp-icicle-kit-es-v2021.04-r0.txt lrwxrwxrwx 2 jaufranc jaufranc 38 Sep 26 18:06 mmc-tftp.txt -> mmc-tftp-icicle-kit-es-v2021.04-r0.txt -rw-r--r-- 2 jaufranc jaufranc 1.6M Sep 26 18:08 modules--5.12.1+git0+ce6fc289da-r0-icicle-kit-es-20210926061423.tgz lrwxrwxrwx 2 jaufranc jaufranc 67 Sep 26 18:08 modules-icicle-kit-es.tgz -> modules--5.12.1+git0+ce6fc289da-r0-icicle-kit-es-20210926061423.tgz -rw-r--r-- 2 jaufranc jaufranc 5.1K Sep 27 09:29 mpfs-dev-cli.env -rw-r--r-- 2 jaufranc jaufranc 5.4G Sep 27 09:46 mpfs-dev-cli-icicle-kit-es-20210927021251.rootfs.ext4 -rw-r--r-- 2 jaufranc jaufranc 103K Sep 27 09:27 mpfs-dev-cli-icicle-kit-es-20210927021251.rootfs.manifest -rw-r--r-- 2 jaufranc jaufranc 5.5G Sep 27 09:50 mpfs-dev-cli-icicle-kit-es-20210927021251.rootfs.wic -rw-r--r-- 2 jaufranc jaufranc 1.4G Sep 27 09:58 mpfs-dev-cli-icicle-kit-es-20210927021251.rootfs.wic.gz -rw-r--r-- 2 jaufranc jaufranc 225K Sep 27 09:27 mpfs-dev-cli-icicle-kit-es-20210927021251.testdata.json lrwxrwxrwx 2 jaufranc jaufranc 53 Sep 27 09:46 mpfs-dev-cli-icicle-kit-es.ext4 -> mpfs-dev-cli-icicle-kit-es-20210927021251.rootfs.ext4 lrwxrwxrwx 2 jaufranc jaufranc 57 Sep 27 09:27 mpfs-dev-cli-icicle-kit-es.manifest -> mpfs-dev-cli-icicle-kit-es-20210927021251.rootfs.manifest lrwxrwxrwx 2 jaufranc jaufranc 55 Sep 27 09:27 mpfs-dev-cli-icicle-kit-es.testdata.json -> mpfs-dev-cli-icicle-kit-es-20210927021251.testdata.json lrwxrwxrwx 2 jaufranc jaufranc 52 Sep 27 09:58 mpfs-dev-cli-icicle-kit-es.wic -> mpfs-dev-cli-icicle-kit-es-20210927021251.rootfs.wic lrwxrwxrwx 2 jaufranc jaufranc 55 Sep 27 09:58 mpfs-dev-cli-icicle-kit-es.wic.gz -> mpfs-dev-cli-icicle-kit-es-20210927021251.rootfs.wic.gz -rwxr-xr-x 1 jaufranc jaufranc 477K Sep 26 22:30 payload.bin lrwxrwxrwx 2 jaufranc jaufranc 36 Sep 26 18:06 u-boot.bin -> u-boot-icicle-kit-es-v2021.04-r0.bin lrwxrwxrwx 2 jaufranc jaufranc 36 Sep 26 18:06 u-boot-icicle-kit-es.bin -> u-boot-icicle-kit-es-v2021.04-r0.bin -rw-r--r-- 2 jaufranc jaufranc 476K Sep 26 18:06 u-boot-icicle-kit-es-v2021.04-r0.bin lrwxrwxrwx 2 jaufranc jaufranc 49 Sep 26 18:06 u-boot-mpfs-initial-env -> u-boot-mpfs-initial-env-icicle-kit-es-v2021.04-r0 lrwxrwxrwx 2 jaufranc jaufranc 49 Sep 26 18:06 u-boot-mpfs-initial-env-icicle-kit-es -> u-boot-mpfs-initial-env-icicle-kit-es-v2021.04-r0 -rw-r--r-- 2 jaufranc jaufranc 3.2K Sep 26 18:06 u-boot-mpfs-initial-env-icicle-kit-es-v2021.04-r0 |

รูปภาพที่ไม่มีการบีบอัดนั้นมีขนาด 5.5GB จึงสามารถใส่ลงในการ์ด SD ขนาด 8GB แต่ขอแนะนำให้ใช้การ์ดขนาด 16GB หรือ 32GB นี่คือคำสั่งที่ Microchip จัดเตรียมไว้ให้เพื่อแฟลชไปยังการ์ด SD:

|

1 |

zcat tmp-glibc/deploy/images/icicle-kit-es/mpfs-dev-cli-icicle-kit-es.wic.gz | sudo dd of=/dev/sdX bs=4096 iflag=fullblock oflag=direct conv=fsync status=progress |

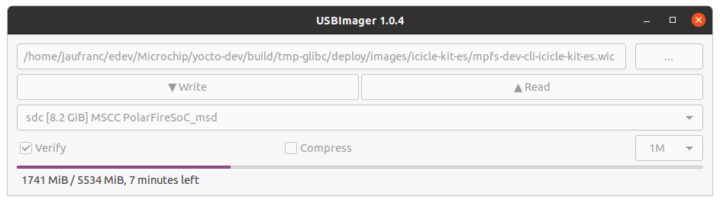

แต่ถ้าคุณต้องการการตรวจสอบรูปภาพ ยูทิลิตี้อย่าง USBImager จะเป็นที่ต้องการมากกว่า นั่นคือสิ่งที่ฉันใช้ในการแฟลชภาพไปยังการ์ด SD ขนาด 32GB จากนั้นจึงเสียบเข้าไปในช่องเสียบการ์ด SD ของบอร์ดพัฒนาเพื่อลองใช้งาน

มาขัดจังหวะการบู๊ตเพื่อตรวจสอบว่าตรวจพบการ์ด SD:

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 |

U-Boot 2021.04 (Sep 26 2021 - 09:16:21 +0000) CPU: rv64imafdc Model: Microchip MPFS Icicle Kit DRAM: 2 GiB MMC: mmc@20008000: 0 In: serial@20100000 Out: serial@20100000 Err: serial@20100000 Net: eth0: ethernet@20112000 Hit any key to stop autoboot: 0 RISC-V # mmcinfo Device: mmc@20008000 Manufacturer ID: 0 OEM: 3432 Name: SD16G Bus Speed: 50000000 Mode: SD High Speed (50MHz) Rd Block Len: 512 SD version 3.0 High Capacity: Yes Capacity: 29.1 GiB Bus Width: 4-bit Erase Group Size: 512 Bytes |

ดีแล้ว ไปต่อ… และไม่สามารถเปลี่ยนเป็นเคอร์เนลได้ ในที่สุดฉันก็รีเฟรชรูปภาพโดยใช้ไบนารีที่ไม่บีบอัด และฉันสามารถเข้าสู่ระบบเทอร์มินัลได้:

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 |

root@icicle-kit-es:~# uname -a Linux icicle-kit-es 5.12.1 #1 SMP Sun Sep 26 08:45:19 UTC 2021 riscv64 riscv64 riscv64 GNU/Linux root@icicle-kit-es:~# df -g df: invalid option -- 'g' Try 'df --help' for more information. root@icicle-kit-es:~# df -f df: invalid option -- 'f' Try 'df --help' for more information. root@icicle-kit-es:~# df -h Filesystem Size Used Avail Use% Mounted on /dev/root 5.2G 4.2G 733M 86% / devtmpfs 817M 0 817M 0% /dev tmpfs 818M 0 818M 0% /dev/shm tmpfs 327M 9.5M 318M 3% /run tmpfs 4.0M 0 4.0M 0% /sys/fs/cgroup tmpfs 818M 0 818M 0% /tmp tmpfs 818M 100K 818M 1% /var/volatile tmpfs 164M 0 164M 0% /run/user/0 root@icicle-kit-es:~# fdisk -l GPT PMBR size mismatch (11334293 != 61067263) will be corrected by write. The backup GPT table is not on the end of the device. Disk /dev/mmcblk0: 29.12 GiB, 31266439168 bytes, 61067264 sectors Units: sectors of 1 * 512 = 512 bytes Sector size (logical/physical): 512 bytes / 512 bytes I/O size (minimum/optimal): 512 bytes / 512 bytes Disklabel type: gpt Disk identifier: 707A61C6-0BE8-405E-BF47-9E8071F3EEC9 Device Start End Sectors Size Type /dev/mmcblk0p1 8192 47009 38818 19M Microsoft basic data /dev/mmcblk0p2 47010 63393 16384 8M BIOS boot /dev/mmcblk0p3 65536 11334259 11268724 5.4G Linux filesystem |

rootfs ไม่ได้ปรับขนาดโดยอัตโนมัติ และดูเหมือนว่าจะมีปัญหากับตาราง GPT… ฉันไม่ค่อยแน่ใจว่าเกิดอะไรขึ้นที่นี่ แต่เนื่องจากรูปภาพที่สร้างขึ้นเองของเราใช้งานได้ และเรามีแฟลช eMMC ให้แฟลชไปที่ที่จัดเก็บข้อมูลภายในแทน

ปิดบอร์ด ถอดการ์ด SD ออก และเชื่อมต่อกับ ttyUSB0 ด้วยBootterm เพื่อเข้าถึงเทอร์มินัล HSS:

|

1 |

bt ttyUSB0 |

ก่อนที่จะรีสตาร์ทบอร์ดพัฒนา ให้ขัดจังหวะการบู๊ต และพิมพ์ “ usbdmsc” เพื่อแสดงหน่วยความจำแฟลช eMMC เป็นที่เก็บข้อมูล USB ขนาดใหญ่บนโน๊ตบุ๊ค Ubuntu ของเรา

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 |

[5.623947] HSS_MMCInit(): Attempting to select eMMC ... Passed Press a key to enter CLI, ESC to skip Timeout in 5 seconds .[6.915522] HSS_ShowTimeout(): Character 32 pressed [6.921945] HSS_TinyCLI_Parser(): Type HELP for list of commands [6.929236] HSS_TinyCLI_Parser(): >> usbdmsc [27.703151] HSS_TinyCLI_Execute(): Unknown command >><<. [27.710094] HSS_TinyCLI_Parser(): >> usbdmsc [37.207116] HSS_MMCInit(): Attempting to select SDCARD ... [38.215220] mmc_init_common(): MSS_MMC_init() returned unexpected 0 Failed [38.223900] HSS_MMCInit(): Attempting to select eMMC ... Passed Waiting for USB Host to connect... (CTRL-C to quit) USB Host connected. Waiting for disconnect... (CTRL-C to quit) 664064 bytes written, 21166080 bytes read |

เราต้องการสาย Micro USB อีกเส้นที่เชื่อมต่อกับพอร์ต J16 Micro USB เพื่อดูหน่วยความจำแฟลชใน Ubuntu

เราสามารถยกเลิกการต่อเชื่อมพาร์ติชั่นการบู๊ตและรูทก่อนที่จะแฟลชอิมเมจเหมือนกับที่เราทำกับการ์ด SD ฉันลองใช้อิมเมจ gz ก่อน แต่ฉันมีปัญหาเดียวกันกับการ์ด SD ฉันไม่สามารถเมานต์พาร์ติชั่นรูทแม้กระทั่งบนพีซี ดังนั้นฉันจึงเลือกอิมเมจที่ไม่บีบอัด และทุกอย่างก็เป็นไปอย่างราบรื่น

หลังจากเสร็จสิ้น เราสามารถถอดสายไมโคร USB ที่เชื่อมต่อกับ J16 และเข้าถึงอิมเมจ Linux ของเรา…

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 |

jaufranc@cnx-laptop-4:~/edev/Microchip/yocto-dev/build$ bt ttyUSB1 Trying port ttyUSB1... Connected to ttyUSB1 at 115200 bps. Escape character is 'Ctrl-]'. Use escape followed by '?' for help. icicle-kit-es login: root root@icicle-kit-es:~# uname -a Linux icicle-kit-es 5.12.1 #1 SMP Sun Sep 26 08:45:19 UTC 2021 riscv64 riscv64 riscv64 GNU/Linux root@icicle-kit-es:~# df -h Filesystem Size Used Avail Use% Mounted on /dev/root 5.2G 4.2G 733M 86% / devtmpfs 817M 0 817M 0% /dev tmpfs 818M 0 818M 0% /dev/shm tmpfs 327M 9.6M 318M 3% /run tmpfs 4.0M 0 4.0M 0% /sys/fs/cgroup tmpfs 818M 0 818M 0% /tmp tmpfs 818M 100K 818M 1% /var/volatile tmpfs 164M 0 164M 0% /run/user/0 root@icicle-kit-es:~# |

สวัสดีชาวโลก Cross-Compilation

เรามาลองคอมไพล์โปรแกรม Hello World กัน

|

1 2 3 4 5 |

#include <stdio.h> int main() { printf("Hello, World!\n"); return 0; } |

สำหรับ RISC-V โดยใช้ Yocto toolchain ซึ่งเราจะเพิ่มในเส้นทางก่อน:

|

1 |

export PATH=$PATH:~/edev/Microchip/yocto-dev/build/tmp-glibc/sysroots-components/x86_64/gcc-cross-riscv64/usr/bin/riscv64-oe-linux |

และใช้เครื่องมือ RISCV GCC เพื่อ build :

|

1 2 3 4 5 |

riscv64-oe-linux-gcc hello.c -o hello hello.c:1:10: fatal error: stdio.h: No such file or directory 1 | #include <stdio.h> | ^~~~~~~~~ compilation terminated. |

อ๊ะ มันไม่ทำงานตามที่คาดไว้ ดูเหมือนว่า toolchain จะติดตั้งไม่ถูกต้อง หรือฉันใช้ผิดอัน ฉันได้ลองใช้ CFLAGS แล้ว แต่ไม่ใช่… บางทีมันอาจจะใช้ได้เฉพาะใน framework ของ Yocto/Bitbake… ฉันมีประสบการณ์มากขึ้นกับ buildroot และโดยปกติ cross-compilation toolchain จะทำงานนอกกรอบ

เกณฑ์มาตรฐาน EEMBC CoreMark

ดังนั้นฉันจะสร้าง EEMBC CoreMark ในเครื่อง นั่นคือสร้างโดยตรงบนบอร์ด รูปภาพที่เราสร้างขึ้นมาพร้อมกับ git และ GNU GCC toolchain ดังนั้นจึงควรตรงไปตรงมา

|

1 2 3 |

https://github.com/eembc/coremark cd coremark/ make -j4 |

Buid และรัน CoreMark ด้วยสองไฟล์ที่สร้างขึ้น

- run1.log

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 |

2K performance run parameters for coremark. CoreMark Size : 666 Total ticks : 14935 Total time (secs): 14.935000 Iterations/Sec : 1339.136257 Iterations : 20000 Compiler version : GCC11.1.0 Compiler flags : -O2 -DPERFORMANCE_RUN=1 -lrt Memory location : Please put data memory location here (e.g. code in flash, data on heap etc) seedcrc : 0xe9f5 [0]crclist : 0xe714 [0]crcmatrix : 0x1fd7 [0]crcstate : 0x8e3a [0]crcfinal : 0x382f Correct operation validated. See README.md for run and reporting rules. CoreMark 1.0 : 1339.136257 / GCC11.1.0 -O2 -DPERFORMANCE_RUN=1 -lrt / Heap |

- run2.log

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 |

2K validation run parameters for coremark. CoreMark Size : 666 Total ticks : 14907 Total time (secs): 14.907000 Iterations/Sec : 1341.651573 Iterations : 20000 Compiler version : GCC11.1.0 Compiler flags : -O2 -DPERFORMANCE_RUN=1 -lrt Memory location : Please put data memory location here (e.g. code in flash, data on heap etc) seedcrc : 0x18f2 [0]crclist : 0xe3c1 [0]crcmatrix : 0x0747 [0]crcstate : 0x8d84 [0]crcfinal : 0xd304 Correct operation validated. See README.md for run and reporting rules. |

เนื่องจากแกน RISC-V ทำงานที่ 600 MHz บอร์ดได้รับคะแนน 1339.136257 หรือประมาณ 2.23 CoreMark/MHz แต่ไมโครชิปรายงาน 3.25 CoreMark/MHzบนบอร์ด ลองอีกครั้งโดยใช้แฟล็กเดียวกับที่บริษัทใช้:

|

1 2 |

make clean make XCFLAGS="-O3 -DHAS_STDIO -DHAS_TIME_H -DUSE_CLOCK -fno-common -funroll-loops -finline-functions -falign-functions=16 -falign-jumps=4 -falign-loops=4 -finline-limit=1000 -fno-if-conversion2 -fselective-scheduling -fno-tree-dominator-opts -lpthread -DHAS_FLOAT=0 -mtune=sifive-7-series" |

นี่คือเนื้อหาของ run1.log:

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 |

2K performance run parameters for coremark. CoreMark Size : 666 Total ticks : 12874295 Total time (secs): 12 Iterations/Sec : 1666 Iterations : 20000 Compiler version : GCC11.1.0 Compiler flags : -O2 -O3 -DHAS_STDIO -DHAS_TIME_H -DUSE_CLOCK -fno-common -funroll-loops -finline-functions -falign-functions=16 -falign-jumps=4 -falign-loops=4 -finline-limit=1000 -fno-if-conversion2 -fselective-scheduling -fno-tree-dominator-opts -lpthread -DHAS_FLOAT=0 -mtune=sifive-7-series -DPERFORMANCE_RUN=1 -lrt Memory location : Please put data memory location here (e.g. code in flash, data on heap etc) seedcrc : 0xe9f5 [0]crclist : 0xe714 [0]crcmatrix : 0x1fd7 [0]crcstate : 0x8e3a [0]crcfinal : 0x382f Correct operation validated. See README.md for run and reporting rules. |

อย่างไรก็ตาม ไม่พบคะแนน CoreMark แต่เรายังคงมี Iterations/Sec ที่เปลี่ยนจาก 1341.651573 เป็น 1666 ดังนั้นจึงได้รับการปรับปรุง ง่ายที่จะดูว่าทำไมคะแนนไม่แสดง แต่ดูจากรหัส:

|

1 2 3 4 5 6 7 8 9 10 11 |

ee_printf( "Correct operation validated. See README.md for run and reporting " "rules.\n"); #if HAS_FLOAT if (known_id == 3) { ee_printf("CoreMark 1.0 : %f / %s %s", default_num_contexts * results[0].iterations / time_in_secs(total_time), COMPILER_VERSION, COMPILER_FLAGS); |

มาทำซ้ำกับ -DHAS_FLOAT=1 แทน…

|

1 |

make clean make XCFLAGS="-O3 -DHAS_STDIO -DHAS_TIME_H -DUSE_CLOCK -fno-common -funroll-loops -finline-functions -falign-functions=16 -falign-jumps=4 -falign-loops=4 -finline-limit=1000 -fno-if-conversion2 -fselective-scheduling -fno-tree-dominator-opts -lpthread -DHAS_FLOAT=1 -mtune=sifive-7-series" |

คราวนี้ดูถูกต้อง:

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 |

2K performance run parameters for coremark. CoreMark Size : 666 Total ticks : 12842191 Total time (secs): 12.842191 Iterations/Sec : 1557.366652 Iterations : 20000 Compiler version : GCC11.1.0 Compiler flags : -O2 -O3 -DHAS_STDIO -DHAS_TIME_H -DUSE_CLOCK -fno-common -funroll-loops -finline-functions -falign-functions=16 -falign-jumps=4 -falign-loops=4 -finline-limit=1000 -fno-if-conversion2 -fselective-scheduling -fno-tree-dominator-opts -lpthread -DHAS_FLOAT=1 -mtune=sifive-7-series -DPERFORMANCE_RUN=1 -lrt Memory location : Please put data memory location here (e.g. code in flash, data on heap etc) seedcrc : 0xe9f5 [0]crclist : 0xe714 [0]crcmatrix : 0x1fd7 [0]crcstate : 0x8e3a [0]crcfinal : 0x382f Correct operation validated. See README.md for run and reporting rules. CoreMark 1.0 : 1557.366652 / GCC11.1.0 -O2 -O3 -DHAS_STDIO -DHAS_TIME_H -DUSE_CLOCK -fno-common -funroll-loops -finline-functions -falign-functions=16 -falign-jumps=4 -falign-loops=4 -finline-limit=1000 -fno-if-conversion2 -fselective-scheduling -fno-tree-dominator-opts -lpthread -DHAS_FLOAT=1 -mtune=sifive-7-series -DPERFORMANCE_RUN=1 -lrt / Heap |

แต่นั่นเป็นเพียง 2.59 CoreMark/Mhz ยังไม่ถึง 3.125 CoreMark/MHz อันที่จริง มันจับคู่ผลลัพธ์ของ Microchip โดยใช้ดัชนีที่ไม่ได้ลงนาม มีคนพยายามทำเช่นเดียวกันและเขาได้รับคำแนะนำให้เปลี่ยนรหัสใน posix/core_portme.h เพื่อใช้ดัชนีที่ลงชื่อ:

|

1 |

typedef signed int ee_u32; |

หลังจากรันการทดสอบประสิทธิภาพอีกครั้ง คะแนนจะยิ่งสูงขึ้น:

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 |

2K performance run parameters for coremark. CoreMark Size : 666 Total ticks : 16767651 Total time (secs): 16.767651 Iterations/Sec : 1789.159376 Iterations : 30000 Compiler version : GCC11.1.0 Compiler flags : -O2 -O3 -DHAS_STDIO -DHAS_TIME_H -DUSE_CLOCK -fno-common -funroll-loops -finline-functions -falign-functions=16 -falign-jumps=4 -falign-loops=4 -finline-limit=1000 -fno-if-conversion2 -fselective-scheduling -fno-tree-dominator-opts -lpthread -DHAS_FLOAT=1 -mtune=sifive-7-series -DPERFORMANCE_RUN=1 -lrt Memory location : Please put data memory location here (e.g. code in flash, data on heap etc) seedcrc : 0xe9f5 [0]crclist : 0xe714 [0]crcmatrix : 0x1fd7 [0]crcstate : 0x8e3a [0]crcfinal : 0x5275 Correct operation validated. See README.md for run and reporting rules. CoreMark 1.0 : 1789.159376 / GCC11.1.0 -O2 -O3 -DHAS_STDIO -DHAS_TIME_H -DUSE_CLOCK -fno-common -funroll-loops -finline-functions -falign-functions=16 -falign-jumps=4 -falign-loops=4 -finline-limit=1000 -fno-if-conversion2 -fselective-scheduling -fno-tree-dominator-opts -lpthread -DHAS_FLOAT=1 -mtune=sifive-7-series -DPERFORMANCE_RUN=1 -lrt / Heap |

1789.159376 CoreMark สอดคล้องกับ 2.98 CoreMark/MHz โดยประมาณ มาทำการแฮ็คครั้งสุดท้ายโดยกำหนด HAS_FLOAT=0 ในบรรทัดคำสั่ง make ผลลัพธ์:

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 |

2K performance run parameters for coremark. CoreMark Size : 666 Total ticks : 16694339 Total time (secs): 16 Iterations/Sec : 1875 Iterations : 30000 Compiler version : GCC11.1.0 Compiler flags : -O2 -O3 -DHAS_STDIO -DHAS_TIME_H -DUSE_CLOCK -fno-common -funroll-loops -finline-functions -falign-functions=16 -falign-jumps=4 -falign-loops=4 -finline-limit=1000 -fno-if-conversion2 -fselective-scheduling -fno-tree-dominator-opts -lpthread -DHAS_FLOAT=0 -mtune=sifive-7-series -DPERFORMANCE_RUN=1 -lrt Memory location : Please put data memory location here (e.g. code in flash, data on heap etc) seedcrc : 0xe9f5 [0]crclist : 0xe714 [0]crcmatrix : 0x1fd7 [0]crcstate : 0x8e3a [0]crcfinal : 0x5275 Correct operation validated. See README.md for run and reporting rules. |

ลองใช้ผลลัพธ์ Iterations/Sec: 1875 เป็นค่า CoreMark 1.0 และในกรณีนี้ เราสามารถบรรลุ 3.125 CoreMark/MHz ได้ตรงตามที่ Microchip ทำ สำหรับการใช้ดัชนีที่ลงนาม เหตุใดการลงนามจึงเร็วกว่าการไม่ได้ลงนามอย่างมาก ฉันไม่แน่ใจ… และเราจำเป็นต้องดูการประกอบ และตรวจสอบจำนวนรอบสำหรับแต่ละคำสั่งเพื่อหาคำตอบ

มันแสดงให้เห็นอย่างแท้จริงว่าสามารถปรับเปลี่ยน/จัดการเกณฑ์มาตรฐานเพื่อให้ได้ผลลัพธ์ที่ดียิ่งขึ้นได้อย่างไร และยังแสดงให้เห็นถึงความสำคัญของการคอมไพล์แฟล็กเพื่อปรับโค้ดให้เหมาะสม หน้าเว็บการวิเคราะห์แรงดัน/กระแสไม่แสดงการเปลี่ยนแปลงที่มีนัยสำคัญใดๆ ระหว่างการทดสอบ

เพียงเท่านี้สำหรับวันนี้ และในอีกไม่กี่สัปดาห์ข้างหน้า ฉันหวังว่าจะโพสต์บางอย่างเกี่ยวกับส่วน FPGA มีคนขอให้ฉันประเมิน virt-io บนบัส PCI-e แต่เนื่องจากข้อจำกัดด้านเวลา ฉันจึงไม่สามารถทำได้ ฉันยังถาม Microchip ที่ตอบว่าควรใช้งานได้ แต่พวกเขายังไม่ได้ทดสอบเลย…

หากคุณสนใจบอร์ดนี้ มีจำหน่ายจากตัวแทนจำหน่ายต่างๆ เช่น Mouser ในราคาไม่ถึง $500 (17,000฿)

แปลจากบทความภาษาอังกฤษ : Getting Started with the Yocto Linux BSP for Polarfire SoC FPGA Icicle Kit

บรรณาธิการข่าวและบทความภาษาไทย CNX Software ได้มีความสนใจในด้านเทคโนโลยี โดยเฉพาะ Smart Home และ IoT