ชิปตระกูล Spartan UltraScale+ FPGA เป็นล่าสุดของการรวมของกลุ่มชิป FPGA ที่เพิ่มประสิทธิภาพด้านต้นทุน ของ AMD ซึ่งเป็นซีรีส์ของ FPGA ที่ออกแบบมาเพื่อให้ราคาเหมาะสมกับต้นทุน พลังงาน และฟอร์มแฟคเตอร์ กลุ่มผลิตภัณฑ์ UltraScale+ FPGA ได้รับการออกแบบมาเพื่อเน้นต้นทุนต่ำและประหยัดพลังงาน โดยมีจำนวนขา I/O มากและมีการรักษาความปลอดภัยระดับสูง

องค์ประกอบในตระกูล Spartan UltraScale+ มีอัตราส่วนขา I/O ต่อ logic cell สูงสุดสำหรับ FPGAs เทคโนโลยีที่ใช้ในการผลิต 28 นาโนเมตรและมีความเร็วในการประมวลผลไม่สูงมาก (สูงสุดในอุตสาหกรรมตามข้อมูลจาก AMD) ใช้พลังงานลดลง 30% เมื่อเปรียบเทียบกับรุ่นก่อนหน้า และมีคุณสมบัติความปลอดภัยที่แข็งแกร่งที่เหนือกว่าส่วนที่เหลือของ Cost-Optimized portfolio

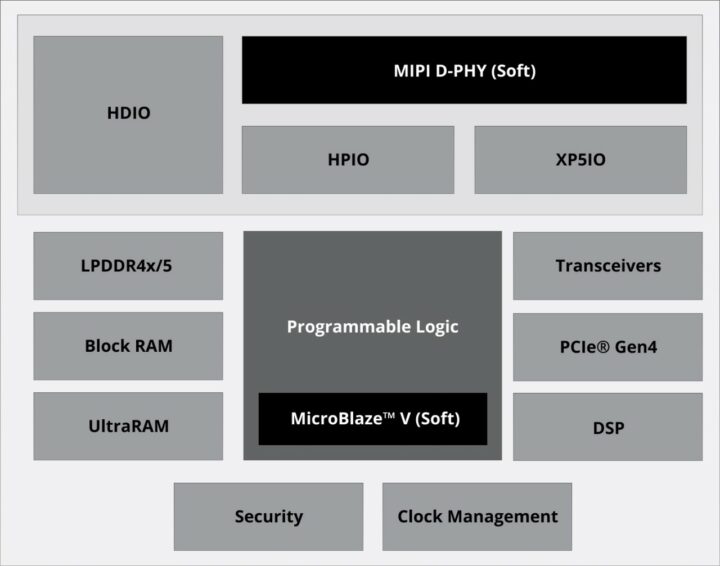

กลุ่ม FPGA นี้สร้างขึ้นโดยใช้สถาปัตยกรรม UltraScale+ แบบเดียวกับผลิตภัณฑ์ Artix และ Zynq รุ่นก่อน เป็น AMD UltraScale+ FPGA รุ่นแรกที่มี hardened DDR memory controller และรองรับ PCIe Gen4 x8 “ให้ทั้งความมีประสิทธิภาพในการใช้พลังงานและความสามารถในการใช้งานสำหรับลูกค้าในอนาคต”

สเปคของ AMD Spartan UltraScale+:

- System Logic Cells– สูงถึง 218K

- หน่วยความจำ

- หน่วยความจำบนชิป: Block RAM สำหรับเวลาแฝงที่ต่ำ (low latency), ปริมาณงานมาก (High throughput) และ UltraRAM

- หน่วยความจำภายนอก: LPDDR4x และ LPDDR5 สูงถึง 4266 Mb/s (hard MC) และ DDR4 (soft MC) IP สูงถึง 2400 Mb/s

- I/O

- จำนวน I/O: 572

- ประเภท:

- High Density I/O (HDIO) สูงสุด 3.3V,

- High-Performance I/O (HPIO) สูงสุด 1.8V,

- XP5IO สูงถึง 1.5V รองรับ 3200 Mb/s MIPI และ 1800 Mb/s LVDS

- PCIe: Gen4 x8

- ตัวรับส่งสัญญาณ – ตัวรับส่งสัญญาณสูงสุด 8 GTH รองรับความเร็วสูงสุด 16.3 Gb/s

- ความปลอดภัย – การใช้งาน cryptography หลังจาก quantum cryptographyที่ได้รับการรับรองจาก NIST, การระบุหมายเลขเฉพาะประจำอุปกรณ์, การใช้การลงโทษที่ถาวรเพื่อป้องกันอุปกรณ์ และการป้องกันการโจมตีผ่านมาตรการป้องกันระบบ DPA

Spartan UltraScale+ FPGA series ออกแบบมาเพื่องาน Embedded Vision, การดูแลสุขภาพ, เครือข่ายอุตสาหกรรม, หุ่นยนต์ และวิดีโอ ตามข่าวประชาสัมพันธ์ จำนวนขา I/O ที่มากจะทำให้ FPGA สามารถเชื่อมต่อกับเซนเซอร์หลายประเภท และโปรแกรมได้เชิงลอจิก (programmable logic) ทำให้สามารถควบคุมเซนเซอร์แบบเรียลไทม์และมีเวลาแฝงต่ำได้

ในด้านซอฟต์แวร์ ตระกูล Spartan UltraScale+ FPGA (รวมถึงส่วนที่เหลือของ AMD FPGA และ adaptive SoCs lineup)) ได้รับการรองรับโดย Vivado Design Suite และ Vitis Unified Software Platform ของ AMD ซึ่งช่วยให้นักออกแบบทั้งฮาร์ดแวร์และซอฟต์แวร์สามารถใช้ “ประโยชน์ของเครื่องมือเหล่านี้ผ่านหน้าจอออกแบบเดียวกันตั้งแต่การออกแบบจนถึงการตรวจสอบ”

ตัวอย่างและ evaluation kits ของ AMD Spartan UltraScale+ คาดว่าจะพร้อมให้ทดลองใช้งานในช่วงในครึ่งปีแรกของปี 2025 มีเอกสารประกอบที่พร้อมใช้งาน และการสนับสนุนเครื่องมือเริ่มต้นด้วยชุด AMD Vivado Suite เริ่มในไตรมาสที่ 4 ปี 2024 สามารถอ่านรายละเอียดเพิ่มเติมเกี่ยวกับตระกูล Spartan UltraScale+ FPGA ที่หน้าผลิตภัณฑ์

แปลจากบทความภาษาอังกฤษ : AMD announces the Spartan UltraScale+ FPGA family for cost-sensitive and IO-intensive applications

บรรณาธิการข่าวและบทความภาษาไทย CNX Software ได้มีความสนใจในด้านเทคโนโลยี โดยเฉพาะ Smart Home และ IoT