ในขณะที่การประชุม RISC-V Summit Europe 2024 กำลังดำเนินอยู่ SiFive ได้ประกาศเปิดตัวซีพียู RISC-V “Essential” รุ่นที่สี่ในกลุ่ม “Essential” (Essential Gen4) ที่มีประสิทธิภาพในการใช้พลังงานที่ดีขึ้นและมีอินเทอร์เฟสที่ยืดหยุ่นมากขึ้นสำหรับ SoC ที่ใช้ในอุปกรณ์แบบฝังตัว (embedded devices)

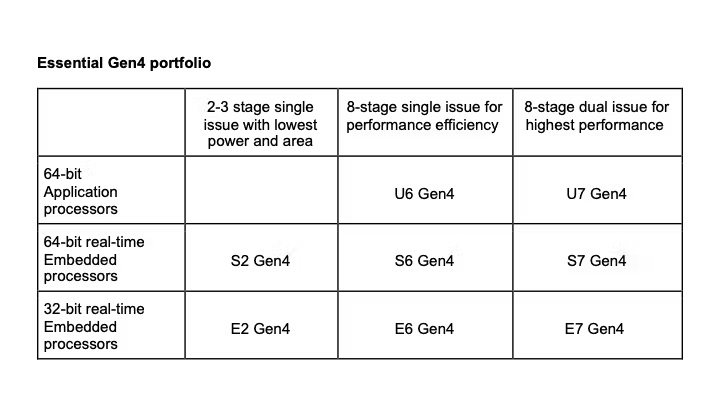

การอัปเดตนี้ครอบคลุมคอร์ RISC-V 32 บิตและ 64 บิต รวมถึงโปรเซสเซอร์แอปพลิเคชัน 64 บิตในซีรีส์ U6 และU7, โปรเซสเซอร์ฝังตัวแบบเรียลไทม์ 64 บิตในซีรีส์ S2, S6, และ S7, และโปรเซสเซอร์ฝังตัวแบบเรียลไทม์ 32 บิตในซีรีส์ E2, E6, และ E7

- ลดการใช้พลังงานขณะทำงานสูงสุดถึง 40%

- 8x ความแตกต่างของคอร์ฝังตัวพื้นฐาน 32 บิตและ 64 บิต

- ตั้งแต่ 2-stage single-issue ไปจนถึง 8-stage superscalar

- ปรับปรุงแคช L2 และเพิ่มประสิทธิภาพหน่วยความจำ L1

- ตัวเลือกการกำหนดค่าและการผสานรวม

- ประเภท, โปรไฟล์ และตัวเลือกของซีพียู

- การเลือกหน่วยความจำบนชิป

- ระบบ, อุปกรณ์ต่อพ่วง, และพอร์ตด้านหน้า

- การจัดการพลังงานและการรักษาความปลอดภัยขั้นสูง

- ดีบักและติดตาม

ด้านซอฟต์แวร์รองรับระบบปฏิบัติการ Embedded Linux และ FreeRTOS และ IDE ที่ใช้ Eclipse สำหรับการพัฒนา C/C++

ด้านบนเป็นประกาศจาก SiFive ที่มีคุณภาพต่ำไม่มีข้อมูลทางเทคนิคและมีเพียงข้อมูลพื้นฐานในข่าวประชาสัมพันธ์ แม้ว่าจะแจ้งว่าสามารถดูข้อมูลเพิ่มเติมที่หน้าผลิตภัณฑ์ แต่ก็ไม่มีข้อมูลสำคัญอยู่ที่นั่น หน้าเอกสารบนเว็บไซต์ก็ไม่มีข้อมูลใดๆ เกี่ยวกับ SiFive Essential Gen4 CPU IP

ดูเหมือนว่ามันถูกเร่งรัดเพื่อการประชุม RISC-V Summit Europe 2024 และเป็นไปได้ที่เขียนขึ้นสำหรับกลุ่มนักลงทุน

แปลจากบทความภาษาอังกฤษ : SiFive announces Essential Gen4 RISC-V CPUs for embedded applications

บรรณาธิการข่าวและบทความภาษาไทย CNX Software ได้มีความสนใจในด้านเทคโนโลยี โดยเฉพาะ Smart Home และ IoT