NXP ได้เปิดตัวโปรเซสเซอร์รุ่นใหม่ i.MX 952 ซึ่งเป็นสมาชิกเพิ่มเติมในตระกูล i.MX 95 series, ออกแบบมาสำหรับงานด้านยานยนต์และอุตสาหกรรมที่ใช้ AI เช่น การตรวจจับผู้ขับขี่, การตรวจจับเด็กในรถ และระบบ HMI ภายในห้องโดยสาร

i.MX 952 มาพร้อมคอร์ประมวลผล Arm Cortex-A55 สูงสุด 4 คอร์ พร้อมด้วย Cortex-M7 และ M33 สำหรับงานไมโครคอนโทรลเลอร์ อีกทั้งยังสอดคล้องกับมาตรฐาน ISO 26262 ASIL B และ SIL2/SIL3 ในด้านความปลอดภัยเชิงฟังก์ชัน ชิปนี้ได้รวม eIQ Neutron NPU สำหรับการประมวลผล AI-based sensor fusion, มี ISP ความเร็ว 500 ล้านพิกเซลต่อวินาที ที่รองรับ RGB-IR, และยังเป็นโปรเซสเซอร์ตัวแรกที่มีฟังก์ชัน local dimming ในตัว เพื่อเพิ่มประสิทธิภาพการแสดงผลของจอ ด้านความปลอดภัยมาพร้อม EdgeLock Secure Enclave ที่รองรับ post-quantum cryptography และเป็นไปตามมาตรฐาน ISO 21434 และ IEC 62443 นอกจากนี้ยังสามารถเชื่อมต่อกับอุปกรณ์ของ NXP อื่น ๆ ได้ เช่น PF09 PMIC, PF53 regulator, Trimension UWB, และ IW693/AW693 Wi-Fi 6/6E SoC ทั้งยังใช้ขา (pin) ร่วมกันได้กับโปรเซสเซอร์ในตระกูล i.MX 95 รุ่นอื่น ๆ อีกด้วย

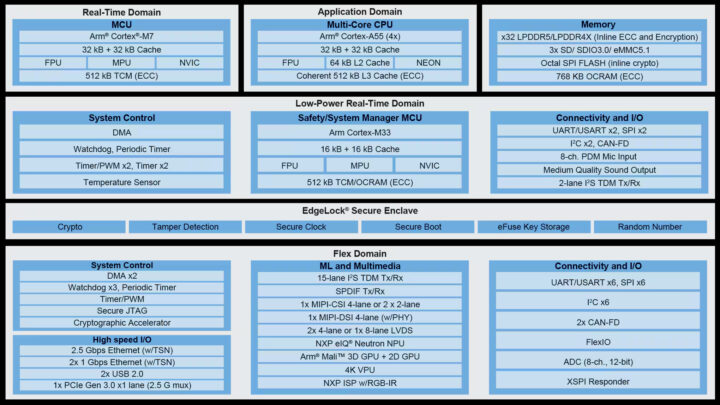

NXP i.MX 952 specifications:

จากบล็อกไดอะแกรมสเปกและคำอธิบายโดยรวม โปรเซสเซอร์ i.MX 952 มีสถาปัตยกรรมแบบ heterogeneous ที่ประกอบด้วยแกนประมวลผล Cortex-A55, Cortex-M7, และ Cortex-M33, รวมถึง eIQ Neutron NPU และ ISP ประสิทธิภาพสูง เช่นเดียวกับรุ่น i.MX 95 แต่เพิ่มคุณสมบัติใหม่ ได้แก่ ฟังก์ชัน local dimming สำหรับจอแสดงผล และ การเข้ารหัสหลังยุคควอนตัม (Post-Quantum Cryptography; PQC) ภายในโมดูลความปลอดภัย EdgeLock Secure Enclave เมื่อเทียบกับรุ่น i.MX 95, รุ่น i.MX 952 มีการปรับลดจำนวนคอร์ของ CPU (จาก 6 เหลือ 4), หน่วยความจำภายใน (on-chip memory), และพอร์ตเชื่อมต่อความเร็วสูงบางส่วน (ไม่มี USB 3.0 และ 10GbE) เพื่อให้ได้สมดุลที่เหมาะสมยิ่งขึ้นระหว่าง ประสิทธิภาพการทำงานและความปลอดภัย (รองรับได้ถึงระดับ SIL 3)

NXP i.MX 952 รองรับระบบปฏิบัติการ Linux และ Android BSPs สำหรับคอร์แอปพลิเคชัน Arm Cortex-A55, ขณะที่คอร์ Cortex-M7 และ Cortex-M33 สำหรับงานเรียลไทม์และงานด้านความปลอดภัยจะรองรับโดย FreeRTOS, eIQ Neutron NPUสามารถใช้งานร่วมกับสภาพแวดล้อมการพัฒนา NXP eIQ machine learning software สำหรับการปรับแต่งโมเดล (optimization), การลดความละเอียด (quantization) และการปรับใช้งาน (deployment) ของงานด้าน AI และ Vision ที่ขอบเครือข่าย (Edge) นักพัฒนายังสามารถใช้เครื่องมือของ NXP เช่น Yocto-based Linux SDK, EdgeLock security framework, MCUXpresso suite เพื่อจัดการการรวมชุดเครื่องมือ (toolchain integration), การตั้งค่า secure boot และการพัฒนาระบบที่เน้นความปลอดภัย (safety-critical) สำหรับแอปพลิเคชันด้านยานยนต์ อุตสาหกรรม และ IoT

หลังจากการเปิดตัวตระกูล i.MX 95 ได้มีบอร์ดพัฒนาและโมดูล SoM หลายรุ่นที่ใช้ชิปนี้ เช่น ADLINK OSM-IMX95, Compulab MCM-iMX95 SoM, Forlinx FET-MX95xx-C (FET-MX9596-C). Toradex Titan Evaluation Kit และอีกหลายรุ่นจากผู้ผลิตรายอื่น ๆ

โปรเซสเซอร์ i.MX 952 ขณะนี้ยังอยู่ในช่วง pre-production และข้อมูลสเปคอาจมีการเปลี่ยนแปลงได้ สามารถดูรายละเอียดเพิ่มเติมได้จากเพจผลิตภัณฑ์ และข่าวประชาสัมพันธ์

แปลจากบทความภาษาอังกฤษ : NXP i.MX 952 processor supports local dimming for AI-enhanced automotive and industrial HMIs

บรรณาธิการข่าวและบทความภาษาไทย CNX Software ได้มีความสนใจในด้านเทคโนโลยี โดยเฉพาะ Smart Home และ IoT