Akeana ก่อตั้งขึ้นเมื่อประมาณสามปีที่แล้ว และเพิ่งเปิดตัวอย่างเป็นทางการพร้อมประกาศผลิตภัณฑ์ซีพียู RISC-V 32 บิตและ 64 บิต และ IP SoC ใหม่ 3 รายการได้แก่ Akeana 100 series สำหรับไมโครคอนโทรลเลอร์ 32 บิต, Akeana 1000 series สำหรับซีพียู 64 บิตพร้อม MMU และAkeana 5000 series ที่มีประสิทธิภาพการทำงานแบบเธรดเดียวสูงกว่าและออกแบบมาเหมาะสำหรับการใช้งานในแล็ปท็อป, Data Center และระบบคลาวด์

บริษัทได้เปิดตัว Scalable Coherent Interconnect, Interrupt Controller และ IOMMU IP สำหรับการสร้างระบบ compute subsystems โดยอิงจาก RISC-V cores, รวมถึงคอร์ Vector RISC-V ที่มุ่งเน้น AI และ IP สำหรับ Matrix Computation โดยทีมออกแบบได้รับรายงานว่ามีประสบการณ์การทำงานกับชิปเซิร์ฟเวอร์ ThunderX2 ของ Marvell มาก่อน

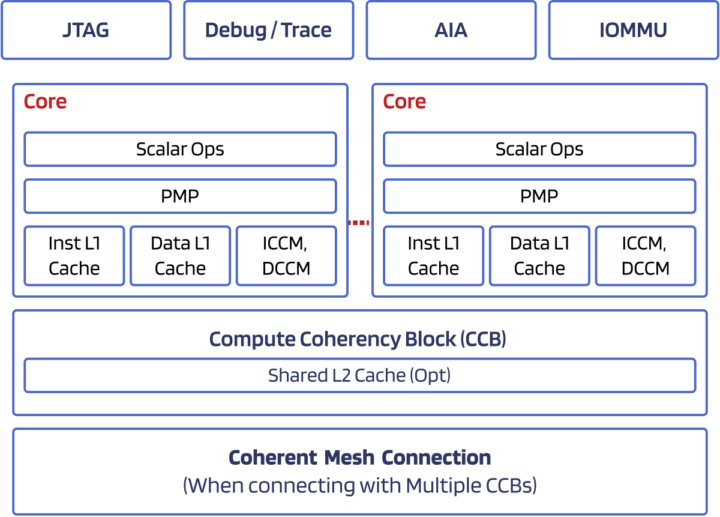

Akeana 100 Series

Akeana 100 Series เป็นกลุ่มผลิตภัณฑ์ซีพียูที่มีการกำหนดค่าได้สูงซึ่งมี RISC-V cores 32 บิต ที่รองรับแอปพลิเคชันตั้งแต่ไมโครคอนโทรลเลอร์แบบ embedded ไปจนถึง edge gateway และอุปกรณ์คอมพิวเตอร์ส่วนบุคคล

มี Akeana 100 RISC-V cores จำนวน 4 รุ่นดังนี้:

- Akeana 110 สำหรับไมโครคอนโทรลเลอร์ที่มีจำกัดพื้นที่และพลังงาน

- L1 I-cache: 8 KB/core

- ชุดคำสั่ง RV32IMAC_Zicsr_Zifencei_Zicbo

- Physical Address range สูงสุด 32 บิต

- in-order pipeline 4-stage

- การออกคำสั่งแบบ Single-width instruction

- ICCM: 16 KB/core

- DCCM: 16 KB/core

- Akeana 120, 130, 140

- ลักษณะทั่วไป

- L1 I-cache: 16 KB/คอร์

- ชุดคำสั่ง RV32IMAC_Zicsr_Zifencei_Zicbo

- Physical Address range สูงสุด 32 บิต

- Physical memory Protection (PMP) พร้อม 8 รายการ

- Akeana 120 สำหรับไมโครคอนโทรลเลอร์ที่จำกัดพื้นที่และพลังงาน

- in-order pipeline 5-stage

- Single-width instruction issue

- ICCM: 64 KB/core

- DCCM: 64 KB/core

- Akeana 130 สำหรับไมโครคอนโทรลเลอร์

- in-order pipeline 9-stage

- Dual instruction issue

- ICCM: 64 KB/core

- DCCM: 64 KB/core

- Branch predictor

- Secondary ALU สำหรับการเพิ่มประสิทธิภาพ

- Akeana 140 สำหรับไมโครคอนโทรลเลอร์ประสิทธิภาพที่เพิ่มขึ้น

- in-order pipeline 9-stage

- Dual instruction issue

- L1 D-cache: 16 KB/core

- ICCM: 512 KB/core

- DCCM: 512 KB/core

- Branch predictor

- Secondary ALU สำหรับการเพิ่มประสิทธิภาพ

- ลักษณะทั่วไป

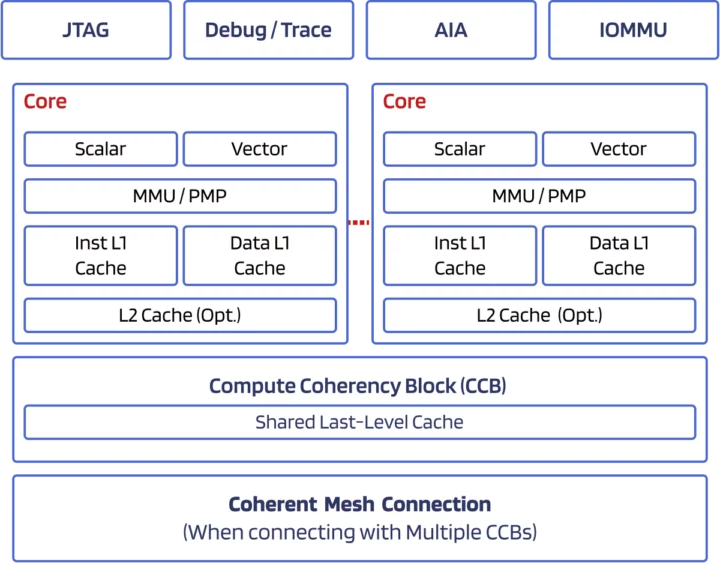

Akeana 1000 Series

Akeana 1000 Series เป็นกลุ่มผลิตภัณฑ์ซีพียูที่ประกอบด้วย RISC-V cores 64 บิตและ MMU เพื่อรองรับระบบปฏิบัติการที่ซับซ้อนในขณะที่ยังคงประหยัดพลังงานและต้องการพื้นที่ชิปน้อย ซีพียูเหล่านี้รองรับไปป์ไลน์แบบเรียงหรือไม่เรียง, มัลติเธรด, การขยายเวกเตอร์, การขยายไฮเปอร์ไวเซอร์ และการขยายอื่นๆ ที่เป็นส่วนหนึ่งของโปรไฟล์ RISC-V ล่าสุดและกำลังจะมีขึ้น (เช่น RVA23) รวมถึงส่วนขยายการคำนวณ AI ที่เป็นทางเลือก

มี Akeana 1000 RISC-V cores จำนวน 3 รุ่นดังนี้:

- ลักษณะทั่วไป

- ชุดคำสั่ง RV64GCB_Zicbo

- โปรไฟล์ RVA22 RISC-V แบบเต็ม

- Single- & double- precision floating-point

- โหมด User

- โหมด Supervisor

- Virtual Address Range 48 bits

- Physical Address Range 39 bits

- สามารถขยายไปยังคลัสเตอร์คอร์หลายตัวที่สอดคล้องกันเต็มรูปแบบ

- ECC support

- AXI/ACE (512 bits)

- Physical memory Protection (PMP) พร้อม 16 entries MU

- Akeana 1100 สำหรับไมโครคอนโทรลเลอร์ระดับ High-end

- in-order pipeline 9-stage

- Dual instruction dispatch

- L1 I-cache: 16 KB/core

- L1 D-cache: 16 KB/core

- MMU พร้อม 256-entry, 4-way TLB

- Akeana 1200 สำหรับ edge gateway SoC

- in-order pipeline 9-stage

- 3-way instruction dispatch

- Secondary ALU ใน pipeline

- L1 I-cache: 32 KB/core

- L1 D-cache: 32 KB/core

- MMU พร้อม 256-entry, 4-way TLB

- Akeana 1300 สำหรับ edge gateway SoC หรือ “Little” core ใน Big/Little configurations ร่วมกับ Akeana 5000 Series cores

- in-order pipeline 12-stage

- 4-way instruction dispatch

- L1 I-cache: 32 KB/core

- L1 D-cache: 32 KB/core

- L2 cache: 256KB

- MMU พร้อม 256-entry, 4-way TLB

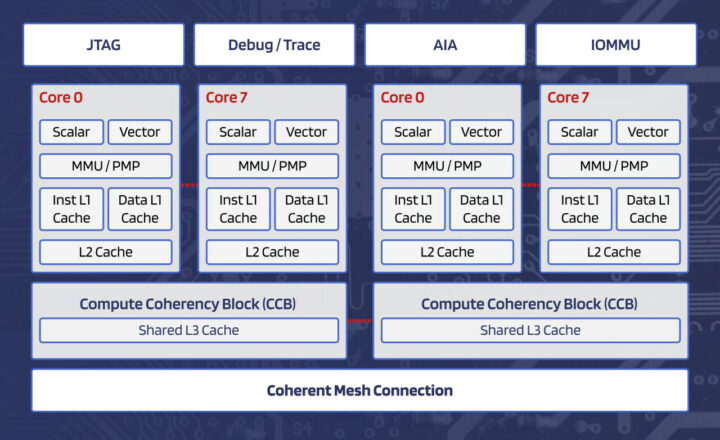

Akeana 5000 Series

Akeana 5000 Series คือกลุ่มผลิตภัณฑ์ซีพียู RISC-V ที่เป็น High-performance ซึ่งบริษัทอ้างว่ามีประสิทธิภาพเหนือกว่า “คู่แข่งที่มีชื่อเสียงและ RISC-V ecosystem” กลุ่มผลิตภัณฑ์นี้มี RISC-V cores 64 บิตที่ปรับให้เหมาะสำหรับการใช้งานในแอปพลิเคชันที่ต้องการประสิทธิภาพสูงในอุปกรณ์รุ่นถัดไป, แล็ปท็อป, Data Center และระบบคลาวด์ ซีพียูเหล่านี้สามารถใช้งานร่วมกับซีรีส์ Akeana 1000 แต่มีประสิทธิภาพการทำงานแบบเธรดเดียวที่สูงกว่ามาก

มี Akeana 5000 RISC-V cores จำนวน 3 รุ่นดังนี้:

- ลักษณะทั่วไป

- ชุดคำสั่ง RV64GCVBK_Zicbo + USH

- โปรไฟล์ RVA23 RISC-V แบบเต็ม

- Single and Double-Precision Floating-Point

- โหมด User

- โหมด Supervisor

- Hypervisor extension

- Vectorextension (128 bits)

- Vector Crypto extension

- 12-stage, out-of-order pipeline

- 48 bits Virtual Address Range

- 256K L2 cache

- สามารถขยายไปยังคลัสเตอร์คอร์หลายตัวที่สอดคล้องกันเต็มรูปแบบ

- รองรับ ECC

- AXI/ACE (512 bits)

- Physical Memory Protection (PMP) พร้อม 16 entries

- MMU

- Akeana 5100 จะใช้เป็น “Big” core ใน Big/Little configurations พร้อม Akeana 1000 Series Little cores

- 4-way instruction dispatch

- L1 I-cache: 32 KB/core

- L1 D-cache: 32KB/core

- Physical Address Space 33 bits

- MMU พร้อม 512-entry, 4-way TLB

- Akeana 5200 จะใช้ใน SoC ของแล็ปท็อปเป็น “Big” core ใน Big/Little configurations พร้อม Akeana 1000 Series Little cores

- 6-way instruction dispatch

- L1 I-cache: 32 KB/core

- L1 D-cache: 32 KB/core

- L2 cache prefetcher

- Physical Address Space 39 bits

- MMU พร้อม 1024-entry, 4-way TLB

- Akeana 5300 – Data Center /แกนประมวลผลโครงสร้างพื้นฐาน

- 8-way instruction dispatch

- L1 I-cache: 64 KB/core

- L1 D-cache: 64 KB/core

- L2 cache prefetcher

- Physical Address Space 39 bits

- MMU พร้อม 2048-entry, 8-way TLB

IP blocks และซอฟต์แวร์อื่น ๆ

บริษัทยังได้เปิดตัว “Processor System IP blocks” ที่จำเป็นสำหรับการออกแบบ SoC รวมถึง Coherent Cluster Cache, I/O MMU, และ IP สำหรับการควบคุมการหยุดชะงัก (Interrupt Controller) นอกจากนี้ Akeana ยังให้บริการ Scalable Mesh และ Coherence Hub IP (ที่เข้ากันได้กับ AMBA CHI) เพื่อสร้าง coherent compute subsystems ขนาดใหญ่ เหมาะสำหรับการใช้งานใน Data Center และกรณีการใช้งานอื่นๆ ในที่สุด AI Matrix computation engine ที่ออกแบบมาเพื่อถ่ายโอนการทำงานของ Matrix Multiply สำหรับ AI acceleration ก็พร้อมให้บริการแล้ว

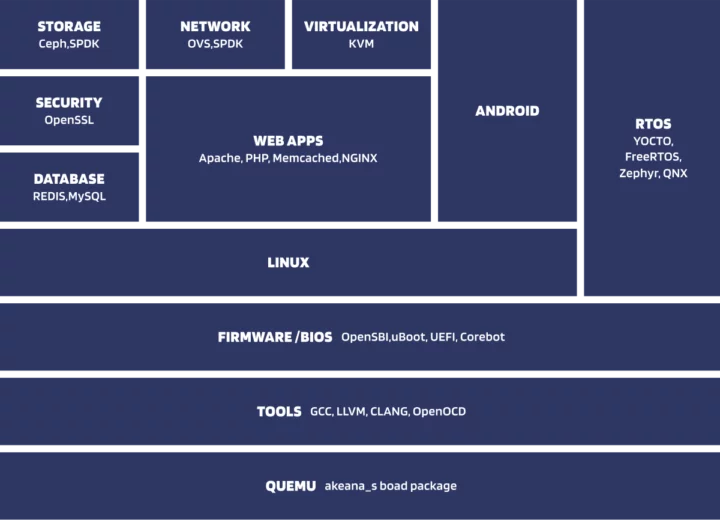

มีข้อมูลจำกัดเกี่ยวกับซอฟต์แวร์ แต่ Akeana ให้บริการ SDK ที่ประกอบด้วย:

เราจะเห็นได้ว่า Android และ Linux ได้รับการรองรับสำหรับซีพียูที่ใช้สำหรับแอปพลิเคชัน และ FreeRTOS, Zephyr และ QNX ได้รับการรองรับสำหรับไมโครคอนโทรลเลอร์

สามารถอ่านข้อมูลเพิ่มเติมได้ที่เว็บไซต์ของบริษัทและประกาศ

แปลจากบทความภาษาอังกฤษ : Akeana unveils 10 RISC-V cores suitable for microcontrollers up to data center chips

บรรณาธิการข่าวและบทความภาษาไทย CNX Software ได้มีความสนใจในด้านเทคโนโลยี โดยเฉพาะ Smart Home และ IoT